Thesis for the degree Doctor of Philosophy

חבור לשם קבלת התואר דוקטור לפילוסופיה

$\mathbf{b}\mathbf{y}$

מאת

Eran Tromer

ערן טרומר

# Hardware-Based Cryptanalysis שבירת צפנים באמצעי חומרה

Advisor

מנחה

Prof. Adi Shamir

פרופ' עדי שמיר

May 2007

אייר תשס"ז

Presented to the Scientific Council of the Weizmann Institute of Science Rehovot, Israel

מוגש למועצה המדעית של מכון ויצמן למדע רחובות, ישראל

### Summary

The theoretical view of cryptography usually models all parties, legitimate ones as well as attackers, as idealized computational devices with designated interfaces, and their security and computational complexity are evaluated in some convenient computational model – usually PC-like RAM machines. This dissertation investigates several cases where reality significantly deviates from this model, leading to previously unforeseen cryptanalytic attacks.

The first part of the dissertation investigates the concrete cost of factoring integers, and in particular RSA keys of commonly used sizes such as 1024 bits. Until recently, this task was considered infeasible (i.e., its cost was estimated as trillions of dollars), based on extrapolations that assumed implementation of factoring algorithms on sequential PC-like computers. We have shown that the situation changes significantly when one introduces custom-built hardware architectures, with algorithms and parametrization that are optimized for concrete technological tradeoffs and do not fit the RAM machine model. Focusing on the Number Field Sieve (NFS) factoring algorithm, we propose hardware architectures for both of its computational steps: the sieving step and the linear algebra step. Detailed analysis and a careful choice of the NFS parameters show that for breaking 1024-bit RSA keys, NFS can be be implemented at a fairly practical cost of a few million US dollars for a throughput of one factorization per year. This casts grave doubt on the security of such cryptographic keys, which are widely deployed in accordance with existing standards and recommendations.

The second part of the dissertation investigates another abstraction violation: side-channel information leakage from cryptographic systems. We demonstrate two such channels. First, cache contention in modern CPUs leads to leakage of information about memory access patterns, and we devise novel ways to exploit this leakage. The new attacks work in pure software, and are applicable even in scenarios where the attacker has no nominal communication channel with the attacked code. They are also extremely efficient; for example, we have demonstrated full recovery of an AES secret key from a Linux encrypted filesystem using just 800 analyzed encryptions, gathered within 65 milliseconds. A second side channel we observe is acoustic emanations: modern PCs produce unintentional acoustic signals that are highly correlated with processor activity, and reveal information about the calculation being performed (e.g., the secret moduli used during RSA decryption). Due to their efficiency and ubiquity, these newly recognized side-channel attacks form a threat in widespread practical circumstances, and thwart many traditional software security measures such as process separation, sandboxes and virtual machines.

### תקציר

הגישה התאורטית לתורת ההצפנה מייצגת את המשתתפים במערכת, בין אם מורשים ובין אם לאו, כמכונות חישוב מופשטות עם ממשק מוגדר, ובוחנת את בטיחותם וסיבוכיותם במודל חישובי נוח כגון מודל דמוי-PC עם זיכרון-גישה-אקראית. דיסרטציה זו חוקרת מספר מקרים בהם המציאות חורגת מגבולות המודל, ובכך פותחת אפשרות לדרכים חדשות לשבירת צפנים.

חלקה הראשון של הדיסרטציה חוקר את העלות של פירוק מספרים לגורמיהם הראשוניים, ובעיקר את המקרה הפרטי של שבירת מערכת ההצפנה RSA עבור מפתחות בגודל נפוץ כגון 1024 ביטים. עד לאחרונה, משימה זו נחשבה לבלתי ישימה (עלותה נחזתה כטריליוני דולרים), בהתבסס על אקסטרפולציה המניחה מימוש מבוסס מחשבים טוריים דמויי PC. הראינו שהמצב שונה מהותית כאשר שוקלים גם ארכיטקטורות חומרה ייעודיות, הנעזרות באלגוריתמים ופרמטרים אשר נבחרו באופן מיטבי על פי שיקולים טכנולוגיים, ואשר חורגות מן המודל החישובי הסדרתי. בהתבסס על אלגוריתם (NFS) Number Field Sieve (NFS) ארכיטקטורות חומרה לשני השלבים העיקריים שבו – שלב הסינון ושלב האלגברה הלינארית. ניתוח מפורט מראה שעבור שבירת מפתחות RSA באורך 1024 ביטים, ניתן לממש את אלגוריתם RSA בעלות מעשית של מיליוני דולרים בודדים עבור תפוקה של פיצוח מפתח בשנה. הדבר מעלה חששות כבדים לבטיחותם של מפתחות אלו, אשר נמצאים בשימוש רחב ומומלצים בתקנים.

חלקה השני של הדיסרטציה עוסק בהפרה נוספת של ההפשטה החישובית: זליגת מידע ממערכות הצפנה דרך ערוצים צדדיים. אנו מציגים שני ערוצים כאלו. הערוץ ראשון הוא תחרות על זכרון המטמון במעבדים מודרניים; זו גוררת זליגת מידע אודות דפוסי גישה לזכרון, ואנו מראים דרכים לניצול זליגה זו לשם שבירת צפנים. ההתקפות החדשות ממומשות בתוכנה וישימות אפילו בתרחישים בהם למתקיף אין אף ערוץ תקשורת נומינלי עם תוכנת ההצפנה המותקפת. ההתקפות המוצגות יעילות ביותר: הדגמנו חשיפה מלאה של מפתח AES סודי מתוך מערכת קבצים מוצפנת של אודות, בלבד. ערוץ נוסף של זליגת מידע הוא זליגות אקוסטיות. מחשבים מודרניים, כך גילינו, פולטים שלא במתכוון רעשים המגלים מידע רב אודות החישוב המתבצע – לדוגמה, אודות מפתחות RSA הסודיים המשמשים לפענות. בשל יעילותן וזמינות יישומן, ההתקפות שזיהינו מהוות איום בקשת רחבה של תרחישים מעשיים, ועוקפות אמצעי בטיחות מקובלים כגון מידור תהליכים ומכונות וירטואליות.

### On the significance of this research

In a society that is becoming increasingly reliant on distributed communication networks, and an economy that is increasingly information-driven, the task of securely channeling information becomes as important as the task of creating it — just as irrigating a field of crop may require not merely the water but also an aqueduct to channel it. The Assyrians of Nineveh built masterful aqueducts to support their "exceedingly great city" [95]; contemporary cryptography builds secure channels of information to fulfill people's needs for trust, privacy and commerce. And as Nineveh fell to hydrological disaster [147], so does a modern peril lie in failure of cryptographic systems.

My research reveals several such imminent risks in well-established cryptographic and security settings. It has shaken the confidence in current deployment of RSA and AES, among the two most prominent cryptographic schemes, in such ubiquitous applications as e-commerce, banking, virtual private networks and encrypted disks. The techniques thus introduced have ramifications to many other cryptographic systems. Recognizing these hithero unknown risks, the computing industry responded by revising its practices and standards (e.g., those of the IEEE [88], Internet RFCs [159][215], USA government [152] and German government [175]) and researching mitigation (e.g., by Intel Corp. [36][37]).

My effective cache-based attacks have unexpectedly felled AES, an encryption algorithm chosen after years of exacting worldwide cryptographic scrutiny; this has spurred much research which extends the attacks and countermeasures described herein. My results on the cost of factoring (and hence the security of RSA) yield concrete estimates that, despite decades of investigation, are a million times lower than previous estimates, thereby showing the poignancy of this approach to custom-hardware cryptanalytic architectures. Numerous works, and a series of dedicated workshops, have since been fruitfully following this path.

### Acknowledgments

Through this maiden voyage of research and discovery, my advisor Adi Shamir served as a compass, a guide and a partner. I am ever indebted for his wise advice, exacting mentorship and unfailing support, as well as for his admirable capacity for sharing his acumen and formidable knowledge. It has been a great privilege to learn the markings of a scientist from him.

I am indebted to my coauthors for our fruitful collaboration: Boaz Barak, Bruce Dodson, James Hughes, Willi Geiselmann, Wil Kortsmit, Paul Leyland, Moni Naor, Asaf Nussboim, Dag Arne Osvik, Ronen Shaltiel, Rainer Steinwandt and Jim Tomlinson — and in particular to Arjen K. Lenstra, for his perspective on computational number theory as well as on the finer aspects of scientific life.

The Weizmann Institute of Science has provided a wondrous environment for learning, cooperation and intellectual growth. I have greatly benefited from, and enjoyed, the conversations with the faculty and other residents of the department, and especially Moni Naor, Oded Goldreich, and Shafi Goldwasser. The institutes's Feinberg Graduate School, under Yosef Yarden and Ami Shalit, has judiciously monitored, supported and awarded my progress. I could not envisage a better place for a budding researcher.

Many other people have contributed to my research by comments, suggestions and discussions: Adi Akavia, Dan Bernstein, Ernie Brickell, Uriel Feige, Andrew Huang, Markus Jakobsson, Robert D. Silverman, Pankaj Rohatgi, Jean-Pierre Seifert, Thorsten Kleinjung, Eran Ofek, Michael Szydlo, David Tromer, Udi Wieder, Gideon Yuval, and numerous others. Dan Boneh, David Brumley, Jens Franke, Thorsten Kleinjung and Herman te Riele provided us with indispensable research data and code. National Instruments Israel donated lab equipment, and Nir Yaniv granted us use of the Nir Space Station studio.

Eli Biham, Shafi Goldwasser, Moni Naor and Omer Reingold graciously served on my interim and final examination committees.

Parts of my research was conducted while at Microsoft Research, hosted by Ramarathnam Venkatesan and Yacov Yacobi.

Back during my studies at the Technion, Erez Petrank and Eli Biham have first instilled in me the appreciation of computational complexity and cryptography; this I shall forever cherish.

My research was conducted, and this thesis written, using a variety of free (libre) software: the Linux kernel, GNU and KDE program suits, the Emacs, Kile and LyX, editors, the teTeX

LATEX typesetting system, the GNU Multiple Precision Library, the Pari/GP and octave numerical/algebraic calculators, the Xfig, OpenOffice Impress and gnuplot drawing/plotting programs, the gcc compiler, the Perl interpreter, and numerous other programs from the the Fedora Core distribution. The OpenSSL and GnuPG cryptographic programs, as well as the Linux kernel, were also employed as test subjects for our cryptanalytic attacks.

I wish to thank my parents, Arie and Zahava, for their ever-present love and support, and for letting me take apart all those gadgets (even though they didn't always fit back together).

My gratitude extends to the many friends and family who helped and bore with me through recent years, and in particular to Yivsam and Zoya Azgad.

In love and appreciation of my wife Shlomit, this dissertation is dedicated to her:

# Summary of contents

| 1  | Hardware-based parallelization of the Number Field Sieve          | 18  |

|----|-------------------------------------------------------------------|-----|

| 1  | Introduction                                                      | 19  |

| 2  | The TWIRL architecture for the NFS sieving step                   | 43  |

| 3  | A mesh-based architecture for the NFS linear algebra step         | 69  |

| 4  | A scalable pipelined architecture for the NFS linear algebra step | 85  |

| 5  | Analysis of NFS parameters                                        | 99  |

| 6  | Conclusions and implications of Part I                            | 123 |

|    |                                                                   |     |

| II | Side-channel attacks                                              | 128 |

| 7  | Introduction                                                      | 129 |

| 8  | Efficient cache attacks on AES                                    | 133 |

| 9  | Acoustic cryptanalysis                                            | 161 |

| 10 | Conclusions and implications of Part II                           | 171 |

## Contents

| $\mathbf{S}$ ι | ımm   | ry                                                    | 2              |

|----------------|-------|-------------------------------------------------------|----------------|

| O              | n the | significance of this research                         | 4              |

| $\mathbf{A}$   | ckno  | vledgments                                            | 5              |

| Li             | st of | Figures                                               | 15<br>17<br>18 |

| Li             | st of | Tables                                                | 17             |

| Ι              | На    | dware-based parallelization of the Number Field Sieve | 18             |

| 1              | Intr  | oduction                                              | 19             |

|                | 1.1   | Overview of Part I                                    | 19             |

|                | 1.2   | Integer factorization                                 | 20             |

|                | 1.3   | Empirical hardness of factorization                   | 22             |

|                |       | 1.3.1 Challenges and past experiments                 | 22             |

|                |       | 1.3.2 1024-bit RSA and its importance                 | 23             |

|                |       | 1.3.3 768-bit RSA and its importance                  | 23             |

|                | 1.4   | Cost measures                                         | 24             |

|                | 1.5   | The Number Field Sieve algorithm                      | 25             |

|                |       | 1.5.1 Background                                      | 25             |

|                |       | 1.5.2 Notation                                        | 25             |

|                |       | 1.5.3 Overview of NFS                                 | 26             |

|   |         | 1.5.4                                                                                   | NFS for discrete logarithms                   | 30                                                       |

|---|---------|-----------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------|

|   | 1.6     | The N                                                                                   | IFS sieving step                              | 30                                                       |

|   |         | 1.6.1                                                                                   | The task                                      | 30                                                       |

|   |         | 1.6.2                                                                                   | Traditional sieving                           | 32                                                       |

|   |         | 1.6.3                                                                                   | Historical sieving devices                    | 33                                                       |

|   |         | 1.6.4                                                                                   | TWINKLE                                       | 34                                                       |

|   |         | 1.6.5                                                                                   | FPGA-based serial sieving                     | 35                                                       |

|   |         | 1.6.6                                                                                   | Mesh-based sieving                            | 35                                                       |

|   |         | 1.6.7                                                                                   | Relation collection without sieving           | 36                                                       |

|   | 1.7     | The N                                                                                   | IFS linear algebra step                       | 36                                                       |

|   |         | 1.7.1                                                                                   | The block Wiedemann algorithm                 | 37                                                       |

|   |         | 1.7.2                                                                                   | Complexity of the block Wiedemann algorithm   | 38                                                       |

|   |         | 1.7.3                                                                                   | The reduced task                              | 40                                                       |

|   |         | 1.7.4                                                                                   | The traditional approach to the matrix step   | 40                                                       |

|   |         | 1.7.5                                                                                   | Bernstein's mesh-based linear algebra circuit | 41                                                       |

| 2 |         |                                                                                         |                                               |                                                          |

|   | The     | TWI                                                                                     | RL architecture for the NFS sieving step      | 43                                                       |

| _ |         |                                                                                         | RL architecture for the NFS sieving step      | <b>43</b>                                                |

| - | 2.1     | Overv                                                                                   | iew                                           | 43                                                       |

| - |         | Overv<br>Basic                                                                          | iew                                           | 43<br>44                                                 |

| - | 2.1     | Overv<br>Basic<br>2.2.1                                                                 | iew                                           | 43<br>44<br>44                                           |

| _ | 2.1     | Overv<br>Basic                                                                          | iew                                           | 43<br>44<br>44<br>46                                     |

| _ | 2.1     | Overv<br>Basic<br>2.2.1<br>2.2.2                                                        | iew                                           | 43<br>44<br>44<br>46<br>50                               |

|   | 2.1 2.2 | Overv<br>Basic<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4                                      | iew                                           | 43<br>44<br>44<br>46<br>50<br>51                         |

|   | 2.1     | Overv<br>Basic<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>Addit                             | iew                                           | 43<br>44<br>44<br>46<br>50<br>51<br>52                   |

|   | 2.1 2.2 | Overv<br>Basic<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4                                      | iew                                           | 43<br>44<br>44<br>46<br>50<br>51                         |

|   | 2.1 2.2 | Overv<br>Basic<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>Addit:<br>2.3.1                   | iew                                           | 43<br>44<br>44<br>46<br>50<br>51<br>52                   |

|   | 2.1 2.2 | Overv<br>Basic<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>Addit:<br>2.3.1<br>2.3.2          | iew                                           | 43<br>44<br>44<br>46<br>50<br>51<br>52<br>52<br>54       |

|   | 2.1 2.2 | Overv<br>Basic<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>Addit:<br>2.3.1<br>2.3.2<br>2.3.3 | iew                                           | 43<br>44<br>44<br>46<br>50<br>51<br>52<br>52<br>54<br>56 |

|   |                                               | 2.3.7                                                                                                  | Testing candidates                                | 59                                                       |

|---|-----------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------|

|   |                                               | 2.3.8                                                                                                  | Lattice sieving                                   | 61                                                       |

|   |                                               | 2.3.9                                                                                                  | Fault tolerance                                   | 61                                                       |

|   | 2.4                                           | Param                                                                                                  | etrization                                        | 62                                                       |

|   |                                               | 2.4.1                                                                                                  | NFS parameters                                    | 62                                                       |

|   |                                               | 2.4.2                                                                                                  | Technology parameters                             | 63                                                       |

|   | 2.5                                           | Cost e                                                                                                 | stimates                                          | 63                                                       |

|   |                                               | 2.5.1                                                                                                  | Cost of sieving for 1024-bit composites           | 63                                                       |

|   |                                               | 2.5.2                                                                                                  | Cost of sieving for 768-bits composites           | 65                                                       |

|   |                                               | 2.5.3                                                                                                  | Cost of sieving for 512-bits composites           | 65                                                       |

|   |                                               | 2.5.4                                                                                                  | Asymptotic behavior for larger composites         | 65                                                       |

|   |                                               | 2.5.5                                                                                                  | Scaling with technology                           | 66                                                       |

|   | 2.6                                           | Compa                                                                                                  | arison to previous works                          | 66                                                       |

|   |                                               |                                                                                                        | ased architecture for the NFS linear algebra step | 69                                                       |

| 3 | A n                                           | nesh-ba                                                                                                | ised architecture for the Nr5 linear algebra step | Uð                                                       |

| 3 | <b>A</b> m 3.1                                | nesh-ba<br>Overvi                                                                                      | •                                                 | 69                                                       |

| 3 |                                               | Overvi                                                                                                 | <u>.</u>                                          |                                                          |

| 3 | 3.1                                           | Overvi<br>Estima                                                                                       | ew                                                | 69                                                       |

| 3 | 3.1<br>3.2                                    | Overvi<br>Estima<br>Basic                                                                              | ew                                                | 69<br>69                                                 |

| 3 | 3.1<br>3.2<br>3.3                             | Overvi<br>Estima<br>Basic                                                                              | ew                                                | 69<br>69<br>71                                           |

| 3 | 3.1<br>3.2<br>3.3                             | Overvi<br>Estima<br>Basic i<br>Choice                                                                  | ew                                                | 69<br>69<br>71<br>73                                     |

| 3 | 3.1<br>3.2<br>3.3                             | Overvit<br>Estima<br>Basic u<br>Choice<br>3.4.1                                                        | ew                                                | 69<br>69<br>71<br>73<br>73                               |

| 3 | 3.1<br>3.2<br>3.3                             | Estima<br>Basic n<br>Choice<br>3.4.1<br>3.4.2<br>3.4.3                                                 | ew                                                | 69<br>69<br>71<br>73<br>73<br>74<br>75                   |

| 3 | 3.1<br>3.2<br>3.3<br>3.4                      | Estima<br>Basic of<br>Choice<br>3.4.1<br>3.4.2<br>3.4.3<br>Improv                                      | ew                                                | 69<br>69<br>71<br>73<br>73<br>74<br>75                   |

| 3 | 3.1<br>3.2<br>3.3<br>3.4                      | Estima<br>Basic r<br>Choice<br>3.4.1<br>3.4.2<br>3.4.3<br>Improve                                      | ew                                                | 69<br>69<br>71<br>73<br>73<br>74<br>75<br>76             |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6        | Estima<br>Basic r<br>Choice<br>3.4.1<br>3.4.2<br>3.4.3<br>Improv                                       | ew                                                | 69<br>69<br>71<br>73<br>74<br>75<br>76<br>78             |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6        | Estima Basic r Choice 3.4.1 3.4.2 3.4.3 Improv Further                                                 | ew                                                | 69<br>69<br>71<br>73<br>74<br>75<br>76<br>78             |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6        | Estima<br>Basic n<br>Choice<br>3.4.1<br>3.4.2<br>3.4.3<br>Improv<br>Further<br>Param<br>3.7.1<br>3.7.2 | ew                                                | 69<br>69<br>71<br>73<br>74<br>75<br>76<br>78<br>79       |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | Estima<br>Basic n<br>Choice<br>3.4.1<br>3.4.2<br>3.4.3<br>Improv<br>Further<br>Param<br>3.7.1<br>3.7.2 | ew                                                | 69<br>69<br>71<br>73<br>74<br>75<br>76<br>78<br>79<br>80 |

| 4 | A s | calable  | e pipelined architecture for the NFS linear algebra step | <b>85</b> |

|---|-----|----------|----------------------------------------------------------|-----------|

|   | 4.1 | Overv    | iew                                                      | 85        |

|   | 4.2 | The a    | rchitecture                                              | 86        |

|   |     | 4.2.1    | A basic scheme                                           | 86        |

|   |     | 4.2.2    | Compressed row handling                                  | 87        |

|   |     | 4.2.3    | Compressed vector transmission                           | 88        |

|   |     | 4.2.4    | Processing vector elements                               | 88        |

|   |     | 4.2.5    | Skewed assignment for iterated multiplication            | 90        |

|   |     | 4.2.6    | Amortizing matrix storage cost                           | 91        |

|   |     | 4.2.7    | Two-dimensional chip array                               | 91        |

|   | 4.3 | Fault    | detection and correction                                 | 92        |

|   |     | 4.3.1    | Importance                                               | 92        |

|   |     | 4.3.2    | A generic scheme                                         | 92        |

|   |     | 4.3.3    | Device-specific considerations                           | 95        |

|   | 4.4 | Param    | netrization                                              | 96        |

|   |     | 4.4.1    | Matrix parameters                                        | 96        |

|   |     | 4.4.2    | Technology parameters                                    | 96        |

|   | 4.5 | Cost     | estimates                                                | 96        |

|   |     | 4.5.1    | Cost for 1024-bit NFS matrix step                        | 96        |

|   |     | 4.5.2    | Further details                                          | 97        |

|   |     | 4.5.3    | Comparison to previous designs                           | 98        |

| 5 | Ana | alysis c | of NFS parameters                                        | 99        |

|   | 5.1 | Overv    | iew                                                      | 99        |

|   | 5.2 | NFS p    | parameter estimation techniques                          | 100       |

|   |     | 5.2.1    | Notes on the Number Field Sieve                          | 100       |

|   |     | 5.2.2    | Extrapolation from asymptotics                           | 102       |

|   |     | 5.2.3    | Semi-smoothness probabilities                            | 103       |

|   |     | 5.2.4    | Estimates via smoothness probabilities                   | 106       |

|   |     | 5.2.5    | Direct smoothness tests                                  | 109       |

|    | 5.3   | Choice of NFS polynomials                                                   |      | 11 | 0 |

|----|-------|-----------------------------------------------------------------------------|------|----|---|

|    |       | 5.3.1 Context                                                               |      | 11 | 0 |

|    |       | 5.3.2 NFS polynomials for RSA-1024                                          |      | 11 | 0 |

|    |       | 5.3.3 NFS polynomials for RSA-768                                           |      | 11 | 2 |

|    | 5.4   | Results for extrapolated parameters                                         |      | 11 | 2 |

|    |       | 5.4.1 Extrapolated parameters                                               | <br> | 11 | 2 |

|    |       | 5.4.2 Evaluation via smoothness probabilities $\dots \dots \dots \dots$     | <br> | 11 | 4 |

|    |       | 5.4.3 Evaluation via actual smoothness tests                                | <br> | 11 | 9 |

|    | 5.5   | The TWIRL sieving parameters                                                | <br> | 12 | 0 |

|    |       | 5.5.1 Yields for RSA-1024                                                   | <br> | 12 | 0 |

|    |       | 5.5.2 Candidates yield in TWIRL                                             | <br> | 12 | 1 |

|    |       | 5.5.3 Optimality and effect of technological progress $\dots \dots \dots$ . | <br> | 12 | 1 |

|    |       | 5.5.4 Yields for RSA-768                                                    | <br> | 12 | 2 |

| 6  | Con   | clusions and implications of Part I                                         |      | 12 | 3 |

|    | 6.1   | Summary of results                                                          | <br> | 12 | 3 |

|    | 6.2   | Notes                                                                       | <br> | 12 | 4 |

|    | 6.3   | Impact and follow-up works                                                  | <br> | 12 | 5 |

| II | Sie   | de-channel attacks                                                          |      | 12 | 8 |

| 7  | Intr  | oduction                                                                    |      | 12 | 9 |

|    | 7.1   | Overview of Part II                                                         |      | 12 | 9 |

|    | 7.2   | Side-channel attacks                                                        |      | 12 | 9 |

|    | 7.3   | Timing attacks                                                              | <br> | 13 | 0 |

| 8  | Effic | cient cache attacks on AES                                                  |      | 13 | 3 |

|    | 8.1   | $Introduction \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                       | <br> | 13 | 3 |

|    |       | 8.1.1 Overview                                                              | <br> | 13 | 3 |

|    |       | 8.1.2 Related work                                                          |      | 13 | 4 |

|    | 8.2   | Preliminaries                                                               |      | 13 | 5 |

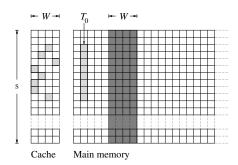

|     | 8.2.1  | Memory and cache structure                     |

|-----|--------|------------------------------------------------|

|     | 8.2.2  | Memory access in AES implementations           |

|     | 8.2.3  | Notation                                       |

| 8.3 | Synchi | ronous known-data attacks                      |

|     | 8.3.1  | Overview                                       |

|     | 8.3.2  | One-round attack                               |

|     | 8.3.3  | Two-rounds attack                              |

|     | 8.3.4  | Measurement via Evict+Time                     |

|     | 8.3.5  | Measurement via Prime+Probe                    |

|     | 8.3.6  | Practical complications                        |

|     | 8.3.7  | Experimental results                           |

|     | 8.3.8  | Variants and extensions                        |

| 8.4 | Async  | hronous attacks                                |

|     | 8.4.1  | Overview                                       |

|     | 8.4.2  | One-Round Attack                               |

|     | 8.4.3  | Measurements                                   |

|     | 8.4.4  | Experimental results                           |

|     | 8.4.5  | Variants and extensions                        |

| 8.5 | Count  | ermeasures                                     |

|     | 8.5.1  | Avoiding memory accesses                       |

|     | 8.5.2  | Alternative lookup tables                      |

|     | 8.5.3  | Data-independent memory access pattern         |

|     | 8.5.4  | Application-specific algorithmic masking       |

|     | 8.5.5  | Cache state normalization and process blocking |

|     | 8.5.6  | Disabling cache sharing                        |

|     | 8.5.7  | Static or disabled Cache                       |

|     | 8.5.8  | Dynamic table storage                          |

|     | 8.5.9  | Hiding the timing                              |

|     | 8.5.10 | Selective round protection                     |

|     | 8.5.11 | Operating system support                       |

| 9             | Aco            | ustic o | cryptanalysis                          | 161 |

|---------------|----------------|---------|----------------------------------------|-----|

|               | 9.1            | Introd  | uction                                 | 161 |

|               |                | 9.1.1   | Overview                               | 161 |

|               |                | 9.1.2   | Related works                          | 161 |

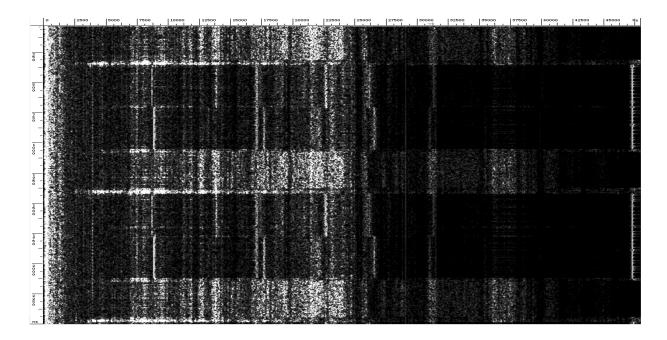

|               | 9.2            | Result  | s                                      | 162 |

|               |                | 9.2.1   | Experimental setup                     | 162 |

|               |                | 9.2.2   | The sound of RSA signatures            | 163 |

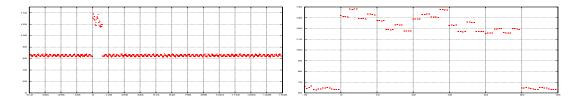

|               |                | 9.2.3   | Distinguishing between RSA secret keys | 164 |

|               |                | 9.2.4   | Timing attacks                         | 165 |

|               |                | 9.2.5   | Instruction pattern differentiation    | 166 |

|               |                | 9.2.6   | Verifying acoustic transduction        | 167 |

|               |                | 9.2.7   | Source of acoustic emanations          | 168 |

|               | 9.3            | Count   | ermeasures                             | 169 |

| 10            | Con            | clusio  | ns and implications of Part II         | 171 |

|               | 10.1           | Summ    | ary of results                         | 171 |

|               | 10.2           | Vulner  | rable cryptographic primitives         | 172 |

|               |                | 10.2.1  | Cache attacks                          | 172 |

|               |                | 10.2.2  | Acoustic attacks                       | 172 |

|               |                | 10.2.3  | Non-cryptographic systems              | 173 |

|               | 10.3           | Attacl  | s scenarios                            | 173 |

|               | 10.4           | Mitiga  | ation                                  | 174 |

|               | 10.5           | Impac   | t and follow-up works                  | 174 |

| Pι            | ıblica         | ations  | and statement of originality           | 177 |

| Bi            | bliog          | graphy  |                                        | 179 |

| $\mathbf{In}$ | dex o          | of nota | ation                                  | 195 |

| In            | $\mathbf{dex}$ |         |                                        | 197 |

# List of Figures

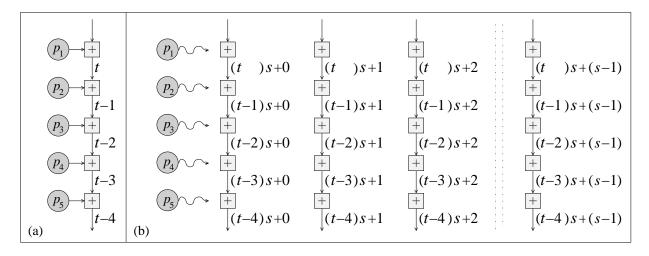

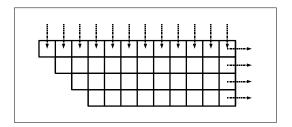

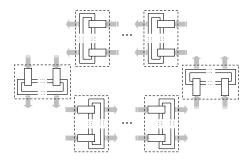

| 2.1 | Flow of sieve locations through devices                                      |

|-----|------------------------------------------------------------------------------|

| 2.2 | Schematic structure of a largish station                                     |

| 2.3 | Schematic structure of a smallish station                                    |

| 2.4 | Schematic structure of a tiny station, for a single progression              |

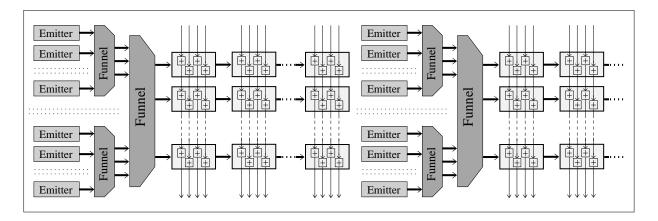

| 2.5 | Schematic structure of an $n$ -to- $m$ funnel                                |

| 3.1 | Realizing a torus in a flat array                                            |

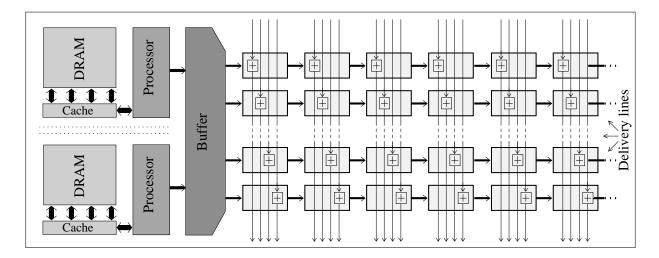

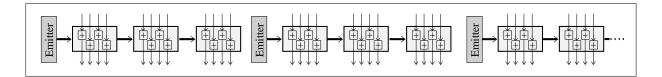

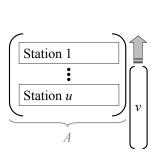

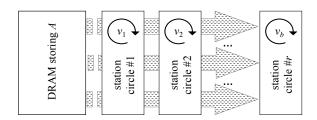

| 4.1 | Distributing the entries of $A$ onto stations                                |

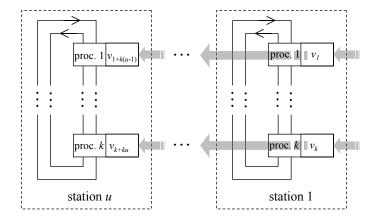

| 4.2 | Subdivision of a chip into stations and processors                           |

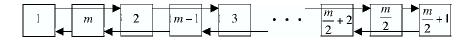

| 4.3 | Arranging the stations into a circle                                         |

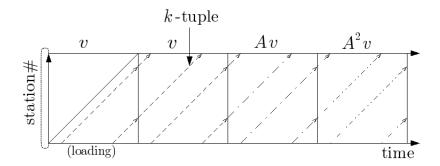

| 4.4 | Movement of vector element $k$ -tuples through the circle of stations        |

| 4.5 | Using external memory to store the matrix                                    |

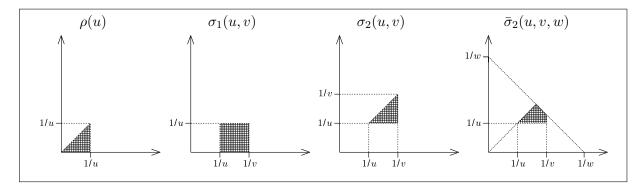

| 5.1 | Illustration of the main (semi-)smoothness probability functions             |

| 8.1 | Schematic of a set-associative cache                                         |

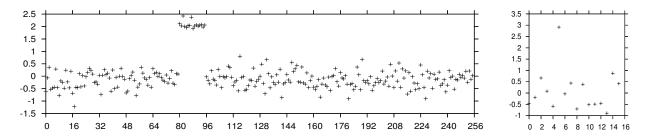

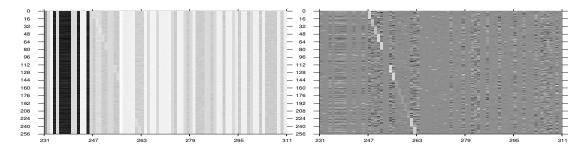

| 8.2 | Candidate scores for a synchronous attack using Prime+Probe measurements 141 |

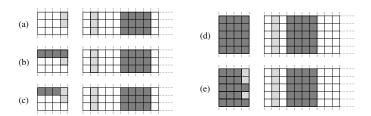

| 8.3 | Schematics of cache states                                                   |

| 8.4 | Timings in Evict+Time measurements                                           |

| 8.5 | Prime+Probe attack                                                           |

| 8.6 | Scores for combinations of key byte candidate and table offset candidate 146 |

| 8.7 | Frequency scores for OpenSSL AES encryption of English text                  |

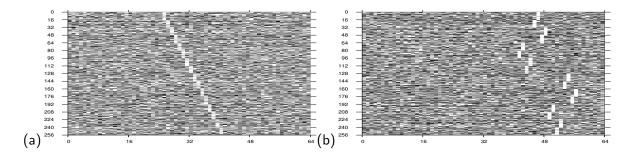

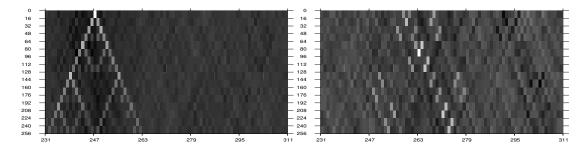

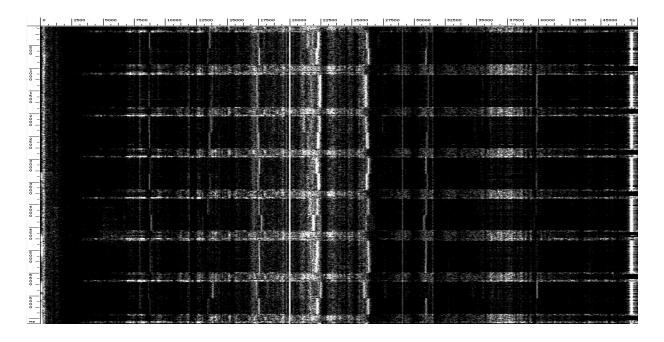

| 9.1 | Acoustic measurement of two identical RSA signatures                         |

LIST OF FIGURES

LIST OF FIGURES

| 9.2 | Acoustic measurement of 7 different RSA signatures              |

|-----|-----------------------------------------------------------------|

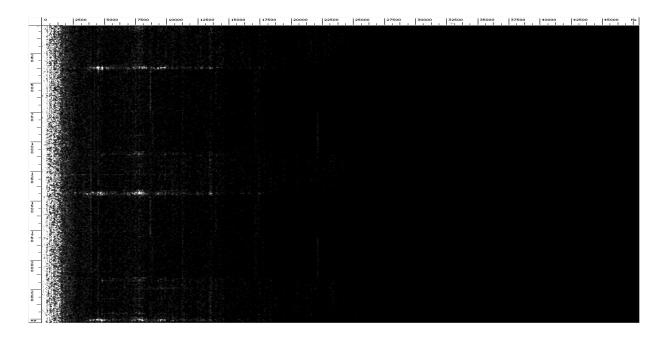

| 9.3 | Acoustic measurement demonstrating temporal resolution          |

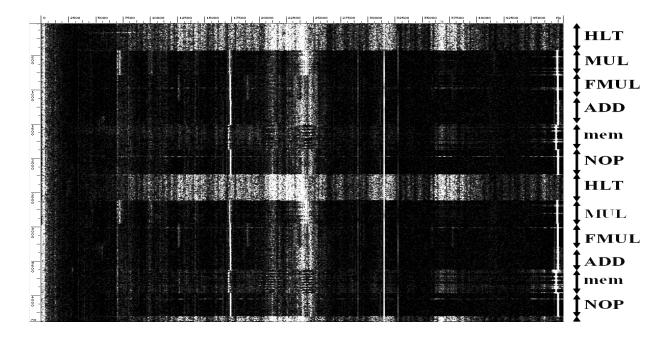

| 9.4 | Acoustic measurement of different CPU instructions              |

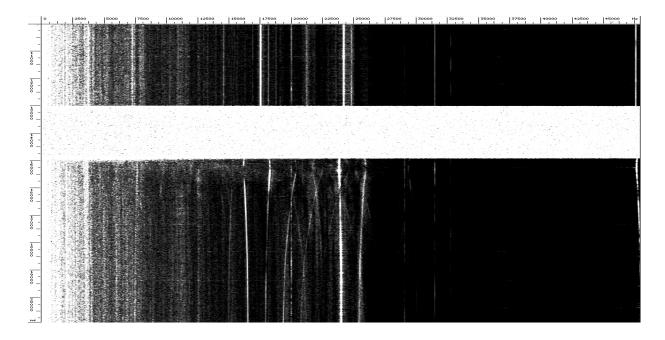

| 9.5 | Acoustic measurement of two identical 4096-bit RSA signatures   |

| 9.6 | Acoustic measurement of a MUL loop during cooling of capacitors |

# List of Tables

| 2.1  | Sieving parameters                                                                         |

|------|--------------------------------------------------------------------------------------------|

| 3.1  | Implementation hardware parameters                                                         |

| 3.2  | Cost of the matrix step for the throughput-optimized matrix                                |

| 3.3  | Cost of the matrix step for the runtime-optimized matrix                                   |

| 3.4  | Cost of the matrix step using a distributed routing-based architecture 83                  |

| 5.1  | Asymptotic behavior of several NFS variants                                                |

| 5.2  | (Semi-)smoothness functions, conditions, notation and terminology $104$                    |

| 5.3  | Estimated yields with polynomials (B)–(F) for extrapolated parameters $\dots \dots 116$    |

| 5.4  | Sieving effort to find $\Pi(2^i,2^{i+1})/32$ ff's for $d=6$                                |

| 5.5  | Minimal sieving efforts to find $T(2^{i_r}, 2^{i_a})/c$ ff's                               |

| 5.6  | Estimated yields of polynomial (A) for extrapolated parameters                             |

| 5.7  | Estimated yields for extrapolated parameters with $\xi^3$                                  |

| 5.8  | Estimated yields for extrapolated smoothness bounds with 6 polynomials $\dots \dots 118$   |

| 5.9  | Actual and estimated number of $(2^i,2^j,1)$ -semismooth $N_{\bf r}(a,b)$ 's for $d=6$ 119 |

| 5.10 | Actual and estimated number of semismooth $N_{\bf a}(a,b)$ 's for $d=6$                    |

| 5.11 | Actual and estimated number of semismooth $N_{\bf a}(a,b)$ 's for $d=6$ (cont.) 120        |

| 5.12 | RSA-1024 parameter sets for TWIRL with 130nm process technology $\dots \dots \dots 121$    |

| 5.13 | RSA-1024 parameter sets for TWIRL with 90nm process technology 122                         |

| 5.14 | RSA-768 parameter sets for TWIRL                                                           |

| 8.1  | Data cache parameters for popular CPU models                                               |

### Part I

# Hardware-based parallelization of the Number Field Sieve

The problem of distinguishing prime numbers from composite numbers and of resolving the latter into their prime factors is known to be one of the most important and useful in arithmetic. It has engaged the industry and wisdom of ancient and modern geometers to such an extent that it would be superfluous to discuss the problem at length. [...]

Furthermore, the dignity of the science itself seems to require that every possible means be explored for the solution of a problem so elegant and so celebrated.

— C. F. Gauss, 1801 [68, article 329]

### Chapter 1

### Introduction

Given any two numbers, we may by a simple and infallible process obtain their product, but it is quite another matter when a large number is given to determine its factors. Can the reader say what two numbers multiplied together will produce the number 8,616,460,799? I think it is unlikely that any one but myself will ever know; for they are two large prime numbers, and can only be rediscovered by trying in succession a long series of prime divisors until the right one be fallen upon.

— W. S. Jevons, 1874 [94, page 141]

#### 1.1 Overview of Part I

Part I addresses the concrete cost of integer factorization and its effect on the security of the RSA cryptosystem. It proposes novel implementations of the Number Field Sieve factoring algorithm, using custom-built hardware devices that achieve massive parallelism, essentially for free. These designs feature an interplay between algorithmic, number-theoretical and technological aspects. By devising algorithms that take advantage of certain properties of the problem and of chip manufacturing technology, efficiency is increased by many orders of magnitude compared to previous proposals. For 1024-bit composites, the resulting cost is a few million US dollars — a millionth of previous predictions, and sufficiently practical to affect industry practice and standards (see §6.3).

The remainder of Chapter 1 surveys the state of the art in integer factorization and its cryptographic significance, and describes past approaches and pertinent works. It also recalls the pertinent details of the Number Field Sieve algorithm, focusing on its two computationally dominant stages, the sieving step and the linear algebra step.

Chapter 2 presents TWIRL, a novel special-purpose architecture for the NFS sieving step. This device is many orders of magnitude more cost-effective than previous proposals, and brings the

sieving step for 1024-bit integers to well within the practical realm: from trillions of US\$ to mere millions

Chapter 3 addresses the NFS linear algebra step, and considers mesh-based hardware architectures for its realization. We begin by briefly evaluating a proposal by Bernstein, showing its practical deficiencies. We then proceed to suggest a different mesh-based algorithms and improve it in various ways, yielding far better scalability and, once again, reducing costs to within the practical realm — albeit with some technological reservations.

Chapter 4 describes an alternative special-purpose device for the NFS linear algebra step. Instead of a mesh, this architecture is based on a pipelined systolic architecture reminiscent of the TWIRL device. It resolves the technological hurdles of the previous approach, further reduces cost, and offers advantages in simulation and verification. We also suggest a highly efficient algorithmic fault detection scheme for the NFS linear algebra step.

Chapter 5 details our analysis of the NFS parameters that will arise when factoring 1024-bit and 768-bit composites, and demonstrate the pi falls one may encounter when following standard techniques. This analysis is necessary for the design and evaluation in preceding chapters. Our analysis indeed shows that the auxiliary steps of NFS can be kept at a cost lower than that of the two major steps addressed above — supporting the implications regarding the practicality of breaking 1024-bit RSA keys.

Chapter 6 summarizes and discusses the results of Part I, and briefly surveys recent progress following our publications.

#### 1.2 Integer factorization

The problem of finding the prime factors of integers is one of the oldest problems in mathematics. Part of its appeal, as put forth by Gauss (see page 18), lies in the elegance and simplicity of the problem's definition: given an integer n, find integers  $p, q \neq \pm 1$  such that n = pq. Despite its simple statement, this has proved to be one of the notoriously difficult problems in computational number theory.<sup>1</sup>

In 1977, the factoring problem gained great significance in cryptography with the introduction of the RSA cryptosystem [176], the first public-key encryption scheme and signature scheme with (conjectured) super-polynomial security. In this cryptosystem, the secret key is a pair of large primes p, q and the public key is their product n = pq; its security thus relies on the hardness of factorization.<sup>2</sup> Subsequently, several other public-key cryptosystems based on the hardness of factoring were proposed (e.g., those of Rabin [172] and Paillier [164]), as well as

<sup>&</sup>lt;sup>1</sup>For the related problem of testing whether a given integer is prime, probabilistic polynomial-time algorithms are known for several decades [141][199][173], and the problem was completely solved by the deterministic polynomial-time algorithm of Agrawal et al. [8].

<sup>&</sup>lt;sup>2</sup>It is not known whether hardness of factorization *suffices* for the security for RSA, but for appropriate parameters this is conjectured to be true.

other cryptographic primitives such as the Blum-Blum-Shub pseudorandom generator [29] and the VSH hash function [46]. To date, the hardness of factorization is one of the few plausible hardness assumptions on which to base public-key cryptography [81], and specifically one of the very few candidate one-way trapdoor permutations [80]. As such, it relates to deep open problems in complexity theory and the foundations of cryptography (e.g., as posed by Impagliazzo<sup>3</sup> [90]).

Beyond the theoretical interest, there is a practical motivation for studying the concrete hardness of integer factorization. RSA, being the most commonly deployed public-key cryptosystem, is ubiquitous in such diverse contexts as secure web sites employing SSL/TLS, S/MIME encrypted e-mail, various e-commerce and banking applications, and code authentication (e.g., web applets, software updates, and game console titles). Hence, all of these presently assume the hardness of integer factorization for their security. As shown in this dissertation, these assumptions are far from warranted.

Various non-trivial algorithms have been devised for integer factorization, starting with observations by Fermat in 1643 [54]. Recent decades have seen especially fruitful, with a cascade of discovered algorithms. One line of development, seeking algorithms whose complexity depends on the size of the composite n, includes Dixon's algorithm, the Continued Fraction method, the Morrison-Brillhart approach, the Quadratic Sieve, and ultimately the Number Field Sieve — along with their many variants. The other line of development is concerned with algorithms whose complexity (for partial factorization, i.e., finding any nontrivial factor) depends only on the size of the smallest factor of n; these include Pollard rho, Pollard p-1, the ultimately the Elliptic Curve method. See the surveys of A. K. Lenstra [125] for a comprehensive survey of modern algorithms, H. C. Williams at al. [218] for a detailed account of historical factorization methods circa 1750–1950, and L. E. Dickson [55] for older methods.

We do not know the true computational complexity of factoring integers drawn from the distributions of interest. The associated decision problem ("does n have a factor smaller than x?") has efficiently-verifiable witnesses (namely the factorization of n), and is thus in  $\mathbf{NP} \cap \mathbf{co}\cdot\mathbf{NP}$ ; consequentially it is believed that factorization is not  $\mathbf{NP}$ -hard, as that would imply a collapse of the polynomial hierarchy. On quantum computers, the problem can be solved in polynomial time via Shor's algorithm [192] [193], but to date little progress has been achieved towards an empirical quantum realization of this algorithm and verification of its scalability.<sup>4</sup> While the problem is widely believed to be hard, this confidence relies solely on the absence of an efficient factoring algorithm despite centuries of research.

The best algorithm known for factoring large integers of a general form is the Number Field Sieve.

<sup>&</sup>lt;sup>3</sup>Impagliazzo [90, §2.5] writes: "Currently, all known secure public key cryptosystems are based on variants of RSA, Rabin, and Diffie-Hellman cryptosystems. If an efficient way of factoring integers and solving discrete logarithms became known, then not only would the popular public key cryptosystems be broken, but there would be no candidate for a secure public-key cryptosystem, or any real methodology for coming up with such a candidate." This largely still holds today, with Diffie-Hellman extended to elliptic curves and with the notable addition of lattice-based cryptosystem such as GGH [82], Ajtai-Dwork [9] and NTRU [85] (see [174] for a partial survey and further pointers). Alas, the latter do not presently enjoy the same level of confidence as factoring.

<sup>&</sup>lt;sup>4</sup>The only such published experiment used a 7-qubit quantum computer to factor  $15 = 3 \cdot 5$ , using inherently non-scalable nuclear magnetic resonance techniques [209].

The (heuristic) asymptotic time and space complexities of NFS are of the form

$$e^{(c+o(1))} (\log n)^{1/3} (\log \log n)^{2/3}$$

where n is the composite being factored, and the constant c depends on the complexity measure and the variant of the algorithm (see  $\S 5.2.1.4$ ). While this algorithm has been fruitfully employed to many a challenging factoring problems (the record stands at 663-bit bits [15][63]), it is not thought to be capable of tackling the factorization problems that arise in practical cryptography, such as factoring 1024-bit RSA keys.

The remainder of this chapter will survey the Number Field Sieve algorithm, its implementations, and concrete factorization experiments and challenges.

#### 1.3 Empirical hardness of factorization

#### 1.3.1 Challenges and past experiments

Factoring integers with current techniques poses significant algorithmic and engineering challenges, and involves considerable uncertainty due to aspects of the algorithm for which analysis is lacking or not tight. Over the past decades, this has led to numerous factorization experiments which employed the state-of-the-art in factoring algorithms and computer technology (of their time) to tackle sample challenges. For composites of a special form suitable to the Special Number Field Sieve, there exist natural challenges such as Fermat numbers [128]. For integers of a general form, which are of greater cryptographic usefulness and which form our focus, it is common to choose targets from the "RSA challenge" list of composites. This list was published by RSA Data Security, Inc. in 1991 and revised in 2001 [177], and consists of essentially randomly-drawn RSA composites (i.e., integers with two prime factors of similar size) whose factorization was not known at the time of publication.<sup>5</sup> The hardness of factoring the RSA challenge composites is widely taken to be representative of the general factoring task for RSA composites of comparable size.

To date, the largest completed experiment (for integers of a general form) has factored the 663-bit composite RSA-200 by Franke et al. [15][63]. Previous records are the 640-bit composite RSA-640 [16], the 576-bit composite RSA-576 [62] and the 530-bit composite RSA-160 [17], by the same group. However, little information has been released about these recent experiments. The best-documented NFS factorization experiment is that of the 512-bit composite RSA-155 [44][43]; we shall at various points rely on empirical information gleaned at that experiment (e.g., in Chapter 5). Prior to that, various smaller composites such as RSA-140 [201] were factored via NFS and its predecessors. More recently, Aoki et al. [12] revisited smaller remaining challenges such as RSA-150 and provided statistics about their factorization via NFS.

<sup>&</sup>lt;sup>5</sup>The process of generating the composites involved knowledge of their factorization, but according to [177], this information (and all potential side-channel information) has been contained and destroyed.

<sup>&</sup>lt;sup>6</sup>See e.g. [35], [44, Table 1] or [197] for a list of factoring records since 1970.

#### 1.3.2 1024-bit RSA and its importance

The present "holy grail" for empirical factorization are 1024-bit composites, exemplified by the RSA-1024 challenge number. RSA keys of this size are very widely deployed, including banking services and the overwhelming majority of secure web sites (including e-commerce hubs such as Amazon and eBay).

Such composites have been posited to be impractical to factor (by conventional means) until 2015 at least. According to Silverman's extrapolation using NFS asymptotics [197] (adjusted to prices circa 2005), completing such a factorization in 1 year would require roughly US\$ 10<sup>12</sup> worth of PC hardware. Brent [35] showed that a high-level extrapolation from past factoring records suggests that 1024-bit composites will be factored no sooner than 2018. Accordingly, until recently a NIST draft guideline [151] suggests 1024-bit RSA keys can be considered secure until 2015 (this was revised [152] to 2010 after the publication of our research, and several industry standards were likewise affected; see §6.3).

Industry leaders appear even more optimistic about the security of such keys. For example, VeriSign Inc., the largest commercial certificate authority, has issued multiple 1024-bit root certificates that are set to expire in 2028. Even RSA Security Inc. distributes a 1024-bit certificate authority keys valid until 2026. These certificates are built into, and trusted by, all major web browsers. If these certificates are compromised prematurely, then browser SSL certificates will become untrustworthy during the many years it would take to revoke all such certificates from users' computers.

Given this motivation, our main focus in the next chapters will be on the cost of factoring 1024-bit composites, and RSA-1024 specifically. To alleviate suspicion, we have duplicated some of the analysis in Chapter 5 using randomly drawn 1024-bit RSA composites instead of RSA-1024; no significant difference in the behavior was detected.

#### 1.3.3 768-bit RSA and its importance

As an intermediate and more accessible goal, and following prior literature (e.g., [197]), we shall at times also consider RSA-768 challenge number [177], as representative of 768-bit RSA composites. RSA keys of this size are of lesser direct practical interest, as they have been mostly phased out, but successfully factoring them is expected to enhance our understanding of the scalability and behavior of the NFS algorithm.

<sup>&</sup>lt;sup>7</sup>For example, certificates named "VeriSign Class {1,2,3,4} Primary CA" in Internet Explorer 6, and likewise certificates with "OU=VeriSign Class {1,2,3} Public Primary Certificate Authority" and "OU=RSA Security 1024 V3" in Firefox 2.0.

1. Introduction 1.4. Cost measures

#### 1.4 Cost measures

Algorithms are traditionally analyzed in terms of their time complexity (number of operations in an abstract model, or concrete running time) and space complexity (amount of storage in some abstract model, or circuit size in some abstract model, or the concrete construction cost of a device). In our focus on very large scale cryptanalytic problems, however, it is often more useful to consider the product of these two costs, known as "AT cost" (for area×time) in VLSI design. We shall refer to this cost measure as throughput cost, to stress its motivation in measuring the equipment cost per unit problem-solving throughput. We shall usually consider it in concrete terms of construction cost and actual running time, e.g., measured in US\$×years.

It appears that throughput cost is indeed appropriate when a large number of problems must be solved during some long period of time while minimizing total expenses. In particular, it is conveniently oblivious to time-space tradeoffs that do not affect that total cost. One should, however, be wary of non-discriminating use in security assessments: an adversary in possession of plans for a device that breaks one key per year and costs \$1M to construct clearly forms a greater menace, compared to an adversary with plans for a device that costs \$1 but requires 1M years of sequential computation per key.

The use of this cost measure in the context of integer factorization was brought to the spotlight by Bernstein [22]. An asymptotic treatment in an abstract model, in several contexts, was given by Wiener [217].<sup>8</sup>

When evaluating special-purpose, custom-built cryptanalytic devices, there are additional costs to consider. Beyond the marginal cost of constructing each device, there are typically significant Non Recurring Engineering (NRE) costs for setting up the production line of the device, e.g., for development, creation and verification of the lithographic masks for a VLSI process. There are also costs involved with power and cooling, physical housing, and maintenance. While these are not our focus, we shall occasionally refer to these considerations as well.

The power and cooling costs reflect the specifics of present technology; in principle any computation can be efficiently implemented using reversible gates and arbitrarily low *total* energy expenditure. However, there exists a physical lower bound on the throughput cost of any fixed algorithm, due to a trade-off between speed and total energy.<sup>9</sup>

<sup>&</sup>lt;sup>8</sup>Notably, Wiener's bounds assume a 3-dimensional circuit whereas the devices discussed here all rely on 2-dimensional VLSI circuits. If considered asymptotically and adapted to 3 dimensions in the natural manner, our devices match Wiener's lower and upper bounds.

$<sup>^9</sup>$ Lloyd [134] shows an upper bound of  $5.43 \cdot 10^{50}$  logical operations per second per kilogram of mass, due to (a variant of) Heisenberg's uncertainty principle. It follows that when performing a given number of operations, the product of mass (hence energy and cost) and time cannot be arbitrarily low.

#### 1.5 The Number Field Sieve algorithm

#### 1.5.1 Background

The Number Field Sieve algorithm was first proposed by J. M. Pollard in 1988, for composites of a special form (this variant is often referred to as the *Special Number Field Sieve*). It was subsequently implemented, improved and extended to the general case in a series of works by A. K. Lenstra, H. W. Lenstra, M. Manasse, C. Pomerance, J. Buhler, L. M. Adleman, P. Montgomery, D. Coppersmith and others. The resulting algorithm is known as the *General Number Field Sieve*, often abbreviated *Number Field Sieve* (NFS). Many additional incremental improvements were suggested during the subsequent two decades. See [129] for an account of the dawn of the NFS and reprints of the seminal works, and [168] for an introduction and historical context.

A full description of the Number Field Sieve taking advantage of all published techniques and variations is rather non-trivial, and to our knowledge no such implementation presently exists. This section describes the parts of the Number Field Sieve algorithm which are relevant to this dissertation. Throughout the discussion, we focus on a common variant of the General Number Field Sieve, which has been employed in many large-scale factoring experiments.

#### 1.5.2 Notation

The following is our basic terminology and notation when discussing the Number Field Sieve. Each of the subsequent chapters introduces its own additional local notation, for discussing architectural parameters (Chapter 2, Chapter 3 and Chapter 4) or number-theoretical functions and additional NFS parameters (Chapter 5). See the Index of notation on page 195.

The number of primes smaller than or equal to x is denoted by  $\pi(x)$ .

Following Knuth and Pardo [107], we denote the prime factors of an integer z>1 by  $z_{(1)}, z_{(2)}, z_{(3)}, \ldots$  where  $|z|=z_{(1)}\cdot z_{(2)}\cdot z_{(3)}\cdots$  and  $z_{(1)}\geq z_{(2)}\geq z_{(3)}\geq \cdots$  are prime or 1.

Let  $x \in \mathbb{Z}$ , U > 0 (a smoothness bound), V > 0 (a large prime bound) and  $\ell$  a non-negative integer. Define the following properties of integers (see also §5.2.3):

An integer z is called U-smooth if  $z_{(1)} \leq U$ , i.e., if all its prime factors are at most U.

More generally, z is called  $(U, V, \ell)$ -semismooth if  $z_{(\ell)} \leq V$  and  $z_{(\ell+1)} \leq U$ , i.e., all its prime factors are smaller than or equal to U except for at most that are smaller than or equal to V; the latter are referred to as large primes.

Lastly, z is called *strictly*  $(U, V, \ell)$ -semismooth if  $U < z_{(\ell)} \le V$  and  $z_{(\ell+1)} \le U$ , i.e., all its prime factors are smaller than or equal to U except for exactly  $\ell$  that are smaller than or equal to V.

Let  $\mathbb{Z}_n \stackrel{\text{def}}{=} \mathbb{Z}/(n\mathbb{Z})\mathbb{Z}_n$  denote the ring of integers modulo n. For a field  $\mathbb{F}$ ,  $\mathbb{F}^{n\times m}$  denotes the ring of  $n\times m$  matrices over  $\mathbb{F}$  and  $\mathbb{F}^n$  denotes the vector space of dimension n over  $\mathbb{F}$ . Matrices shall be denotes by capital Latin letters (e.g., A). Column vectors are written as  $\vec{v}$ , and vector

transposition is denoted  $\vec{v}^{\mathsf{T}}$ . For a vector  $\vec{v}$ , both  $v_i$  and  $(\vec{v})_i$  denote its *i*-th element of  $\vec{v}$ ; but  $\vec{v}_i$  is just some other vector.

The natural logarithm is denoted by  $\ln(x)$  and the logarithm to base 2 by  $\lg(x)$ . Let  $\exp(x) = e^x$ , and let  $x \in y$  denote  $x \cdot 10^y$  (e.g., 1.2E3). The cardinality of a set S is denoted |S|. We use the standard "Big-O" notations O(x), o(x) and  $\tilde{O}(x)$ , where the latter disregards polylogarithmic factors.

In our concrete cost estimates, where not specified otherwise the "\$" currency is US\$ circa 2004. In several places we will use notation such as  $\langle\!\langle x\rangle\!\rangle$  to denote concrete parameters or costs; these will be explained in the relevant context.

#### 1.5.3 Overview of NFS

Let n be the number to be factored. We begin by choosing two irreducible polynomials,  $f(X), g(X) \in \mathbb{Z}[X]$ , that have no common root over  $\mathbb{Z}$ , but share a common root m modulo n:

$$f(m) \equiv g(m) \equiv 0 \pmod{n}$$

.

Let  $\alpha$  be a complex root of f, and consider the ring  $\mathbb{Z}[\alpha]$  of polynomials in  $\alpha$  with integers coefficients (it is homomorphic to  $\mathbb{Z}[X]/(f(X))$ ). Since  $f(\alpha) = 0$  in  $\mathbb{Z}(\alpha)$  and f(m) = 0 in  $Z_n$ , the mapping  $\alpha \mapsto m$  induces a ring homomorphism  $\phi : \mathbb{Z}[\alpha] \to \mathbb{Z}_n$ . Analogously, letting  $\beta$  be a complex root of g, the mapping  $\beta \mapsto m$  induces a ring homomorphism  $\psi : \mathbb{Z}[\beta] \to \mathbb{Z}_n$ .

Suppose we were able to find a finite set of coprime integers,  $\mathcal{T} \subset \mathbb{Z} \times \mathbb{Z}$ , and elements  $\gamma \in \mathbb{Z}[\alpha]$  and  $\delta \in \mathbb{Z}[\beta]$ , such that

$$\prod_{(a,b)\in\mathcal{T}} (a-\alpha b) = \gamma^2 \quad , \qquad \prod_{(a,b)\in\mathcal{T}} (a-\beta b) = \delta^2 \quad . \tag{1.1}$$

Applying the ring homomorphisms  $\phi$  and  $\psi$  on the left and right equations respectively, this yields:

$$\prod_{(a,b)\in\mathcal{T}} (a-mb) = \phi(\gamma)^2 \quad , \qquad \prod_{(a,b)\in\mathcal{T}} (a-mb) = \psi(\delta)^2$$

over  $\mathbb{Z}_n$ . Denoting  $x = \phi(\gamma)$  and  $y = \psi(\delta)$ , we have thus obtained the congruence

$$x^2 \equiv y^2 \pmod{n} \ .$$

If n factors as n = pq with  $p, q \neq \pm 1$  (not necessarily prime) and the choice of  $\mathcal{T}$  was sufficiently random (in a heuristic sense), then with probability at least 1/2 one of these holds:  $x = y \pmod{p}$ ,  $x = -y \pmod{q}$ ; or  $x = -y \pmod{p}$ ,  $x = y \pmod{q}$ . In either of these cases,  $\gcd(n, x - y)$  is a nontrivial factor of n; otherwise we retry with a different  $\mathcal{T}$ . Finally, if  $\gcd(n, x - y)$  or  $n/\gcd(n, x - y)$  are not prime, they can be factored recursively.

The crux of this algorithm is finding a set  $\mathcal{T}$  which fulfills (1.1), i.e., for which  $\prod_{(a,b)\in\mathcal{T}}(a-\alpha b)$  and  $\prod_{(a,b)\in\mathcal{T}}(a-\beta b)$  are both squares in the respective rings.

Following the approach of Morrison-Brillhart and Dixon (see [129]), this problem is reduced to two main steps, a *sieving step* and a *linear algebra step*. These two steps dominate the computational complexity of the NFS, and as such form our focus; we shall discuss them in detail in subsequent sections. The overall procedure for finding  $\mathcal{T}$  is as follows.

Fix rational smoothness and semismoothness bounds  $U_{\mathbf{r}}$  and  $V_{\mathbf{r}}$  respectively, with  $U_{\mathbf{r}} \leq V_{\mathbf{r}}$ . Likewise, fix algebraic smoothness and semismoothness bounds  $U_{\mathbf{a}}$  and  $V_{\mathbf{a}}$ , with  $U_{\mathbf{a}} \leq V_{\mathbf{a}}$ . Fix the number of large primes:  $\ell_{\mathbf{a}}$  on the rational side and  $\ell_{\mathbf{r}}$  on the algebraic side.

**Norms.** Assume for simplicity that f and g are monic and g is linear. <sup>10</sup> For coprime integers (a,b) with  $b \neq 0$ , we define the rational norm and algebraic norm as

$$N_{\mathbf{r}}(a,b) \stackrel{\text{def}}{=} |a-bm|$$

,  $N_{\mathbf{a}}(a,b) \stackrel{\text{def}}{=} |b^d f(a/b)|$  .

**Sieving.** In the sieving step (also called relation collection) we look for relations: pairs of coprime integers (a,b) with b>0 such that  $N_{\bf r}(a,b)$  is  $(U_{\bf r},V_{\bf r},\ell_{\bf r})$ -semismooth and  $N_{\bf a}(a,b)$  is  $(U_{\bf a},V_{\bf a},\ell_{\bf a})$ -semismooth. If  $N_{\bf r}(a,b)$  is  $U_{\bf r}$ -smooth and  $N_{\bf a}(a,b)$  is  $U_{\bf a}$ -smooth, the relation is referred to as a full relation, otherwise it is called a partial relation.

Approximately  $\pi(\min\{U_{\mathbf{r}}, U_{\mathbf{a}}\})/d!$  full relations are *free*, namely one for each prime  $p \leq \min(U_{\mathbf{r}}, U_{\mathbf{a}})$  such that f has d roots modulo p (see [129]).

For non-negative integers  $\ell'_{\mathbf{r}}$  and  $\ell'_{\mathbf{a}}$ , a non-free relation (a,b) for which  $N_{\mathbf{r}}(a,b)$  is strictly  $(U_{\mathbf{r}},V_{\mathbf{r}},\ell'_{\mathbf{r}})$ -semismooth and  $N_{\mathbf{a}}(a,b)$  is strictly  $(U_{\mathbf{a}},V_{\mathbf{a}},\ell'_{\mathbf{a}})$ -semismooth is called an  $(\ell'_{\mathbf{r}},\ell'_{\mathbf{a}})$ -partial relation. We use the standard abbreviations ff for (0,0)-partial ("full,full") relations, fp for (0,1)-partial ("full,partial") relations, fp for (1,0)-partial relations and pp for (1,1)-partial relations.

On the rational side, the sieving step involves sieving with the rational factor base: the set of primes  $p \leq U_{\mathbf{r}}$ , whose cardinality is  $\pi(U_{\mathbf{r}})$ . On the algebraic side, sieving involves an algebraic factor base: the set of pairs (p, r) with  $p \leq U_{\mathbf{a}}$  prime and  $f(r) \equiv 0 \mod p$ , whose cardinality  $\approx \pi(U_{\mathbf{a}})$ . These factor bases and parameters determine the progressions and thresholds in the sieving procedure detailed in §1.6

The part of the (a,b)-plane where relations are sought, called the sieving region, is

$$S \stackrel{\text{def}}{=} \{(a,b) \mid -A < a \le A, \ 0 < b \le B\}$$

for appropriately chosen bounds A, B > 0.<sup>11</sup> The ratio  $\omega \stackrel{\text{def}}{=} A/B$  is called the *skewness ratio* of the sieving region. We denote the size of the sieving region by  $S \stackrel{\text{def}}{=} |\mathcal{S}| = 2AB$ . For any fixed

<sup>&</sup>lt;sup>10</sup> For general g(x) we redefine  $N_{\mathbf{r}}(a,b) \stackrel{\text{def}}{=} |b^{\deg(g)} \cdot g(a/b)|$  (the above is a special case); however this general case entails some complications that are not relevant in our context, so for simplicity we will mostly ignore this extension, and use it only in §5.3 for the special case of non-monic linear g(X) and, implicitly, when referring to Coppersmith's variant in §5.2.1.3 and §5.4.2.3.

<sup>&</sup>lt;sup>11</sup>Such a rectangular sieving region is in general not optimal: a carefully chosen and somewhat smaller region, taking into account the real roots of f, can yield the same number of relations (see [196]). For our yield computations, the effect is minor.

$0 < b \le B$ , the subset

$$\{(a,b) \mid -A < a \le A\}$$

is called a sieve line, and the sieve line width is  $R \stackrel{\text{def}}{=} 2A$ .

Cycles. A cycle is a set C of relations such that  $\prod_{(a,b)\in C} N_{\mathbf{r}}(a,b)$  is a square times a  $U_{\mathbf{r}}$ -smooth number and, simultaneously,  $\prod_{(a,b)\in C} N_{\mathbf{a}}(a,b)$  is a square times a  $U_{\mathbf{a}}$ -smooth number  $^{12}$ . For example, a full relation forms a cycle of length 1. Two (1,0)-partial relations whose rational norms share a large prime can be combined into a cycle of length 2. Similarly, for two (0,1)-partial relations  $(a_1,b_1)$  and  $(a_2,b_2)$  whose algebraic norms share the large prime p, a length 2 cycle follows if the relations correspond to the same root of p mod p, i.e., if p in p in p in p large primes with corresponding roots.

Combining relations into cycles. We say that a set of cycles is *independent* if the characteristic vectors of the cycles (as sets of relations) are linearly independent. Various techniques can be used to construct independent cycles from relations; see [43] for an account. The number of constructable independent cycles of small length clearly grows as additional relations are found, but the expected growth rate is imperfectly understood, especially when many large primes are allowed (large  $\ell_{\bf a}$  and  $\ell_{\bf r}$ ).<sup>13</sup> In Chapter 5 we shall rely on some heuristic and experimental estimates to address this.

Combining cycles into  $\mathcal{T}$ . For a cycle C, define  $\sigma_C = \prod_{(a,b)\in C} (a-\alpha b)$ . In the number field  $\mathbb{Q}(\alpha)$ , the principal ideal generated by  $\sigma_C$  can be uniquely factored into a product of prime ideals:  $\sigma_C = \prod I_i^{q_{C,i}}$ , where  $I_i$  are the prime ideals in  $\mathbb{Q}(\alpha)$  (in arbitrary enumeration) and the  $q_{C,i}$  are integers. This induces an infinite exponent vector  $\vec{q}_C = (q_{C,1}, q_{C,2}, \ldots)$ . Similarly, for any set T' of cycles, the product  $\sigma_T = \prod_{C \in T'} \sigma_C$  has an exponent vector  $\vec{q}_T = \prod_{C \in T'} \vec{q}_C$ . By unique factorization into prime ideals,  $\sigma_T$  is a square iff all the elements of  $\vec{q}_T$  are even. And if  $\sigma_T$  is a square then the set  $T = \bigcup_{C \in T'} C$  (as a union with multiplicity), fulfills the left side of (1.1). It follows that, given many cycles, we can try fulfilling (1.1) by computing their exponent vectors and finding a linear combination whose sum is 0 modulo 2.

Here a crucial observation is made, in order to step from number fields down to mere integers: the factorization of the ideal generated by  $\sigma_C$  into prime ideals of  $\mathbb{Q}(\alpha)$  is closely related to factorization of the integer  $x_C = \prod_{(a,b) \in C} N_{\mathbf{a}}(a,b)$  into prime numbers. This follows from the fact that  $N_{\mathbf{a}}(a,b)$ , as defined above, is the norm of  $a-\alpha b$  in the number field, and has useful properties such as multiplicativity. Very roughly speaking, each prime ideal in the factorization of the ideal generated by  $\sigma_C$  is associated with some prime factor of  $x_C$ . Thus, instead of the exponent vectors  $\vec{q}_C$ , we can consider the exponent vectors  $\vec{r}_C = (r_{C,1}, r_{C,2}, \ldots)$  defined by

<sup>&</sup>lt;sup>12</sup>The condition on  $\prod_{(a,b)\in C} N_{\mathbf{a}}(a,b)$  is slightly more involved, but this is inconsequential in our context; see [129] for the exact characterization.

<sup>&</sup>lt;sup>13</sup>For details see Lenstra and Dodson's experiment, Lambert's partial analysis [113], and Cavallar's methods and results for RSA-155 [43].

factorization over the integers:  $x_C = \prod p_i^{r_{C,i}}$ , where  $p_i$  are the prime numbers (in increasing order) and the  $r_{C,i}$  are integers.<sup>14</sup>

For each cycle C found earlier, we know the exponent vector  $\vec{r}_C$ . We wish to find a linear combination of these exponent vectors with all-even entries. By definition of a cycle, we know that all but the first  $\pi(U_{\mathbf{a}})$  entries of every  $\vec{r}_C$  are even, so we only have to deal with finite-length truncated vectors containing  $\pi(U_{\mathbf{a}})$  entries.

Everything that has been said about also holds on the rational side, i.e., for the norm  $N_{\mathbf{r}}(a, b)$  and the number field  $\mathbb{Q}(\beta)$ . Since we wish to satisfy both terms in (1.1), our task thus boils down to constructing a concatenated exponent vectors (of dimension  $\pi(U_{\mathbf{r}}) + \pi(U_{\mathbf{a}})$ ) for each cycle, and then finding a linear relation modulo 2 among these cycles.

Recall that  $\pi(\min\{U_{\mathbf{r}}, U_{\mathbf{a}}\})/d!$  full relations were obtained for free, so once sieving has created more than  $\Pi(U_{\mathbf{r}}, U_{\mathbf{a}}) \stackrel{\text{def}}{=} \pi(U_{\mathbf{r}}) + \pi(U_{\mathbf{a}}) - \pi(\min\{U_{\mathbf{r}}, U_{\mathbf{a}}\})/d!$  (independent) cycles, we are guaranteed that a linear relation modulo 2 will exist among the corresponding vectors. Thus, the purpose of the sieving step is to find enough relations so that we can construct approximately  $\Pi(U_{\mathbf{r}}, U_{\mathbf{a}})$  independent cycles.